# THE CASE FOR HARDWARE OVERPROVISIONED SUPERCOMPUTERS

by

Tapasya Patki

Copyright © Tapasya Patki 2015

A Dissertation Submitted to the Faculty of the

DEPARTMENT OF COMPUTER SCIENCE

In Partial Fulfillment of the Requirements For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

# THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Tapasya Patki entitled The Case for Hardware Overprovisioned Supercomputers and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy.

|                                                                                                                                                                                                                                           | Date: 7 July 2015                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| David K.Lowenthal                                                                                                                                                                                                                         |                                              |

| Saumya K. Debray                                                                                                                                                                                                                          | Date: 7 July 2015                            |

| John H. Hartman                                                                                                                                                                                                                           | Date: 7 July 2015                            |

| Barry L. Rountree                                                                                                                                                                                                                         | Date: 7 July 2015                            |

| Martin W. J. Schulz                                                                                                                                                                                                                       | Date: 7 July 2015                            |

| Final approval and acceptance of this dissertation is consubmission of the final copies of the dissertation to the GI hereby certify that I have read this dissertation preparecommend that it be accepted as fulfilling the dissertation | raduate College. ared under my direction and |

| Dissertation Director: David K. Lowenthal                                                                                                                                                                                                 | Date: 7 July 2015                            |

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at the University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the copyright holder.

SIGNED: Tapasya Patki

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor Dr. David Lowenthal for his technical guidance, encouragement and relentless support over the years. Dave gave me the freedom to explore new ideas, motivated me to seek depth in my research, taught me how to ask the right questions, and helped me overcome challenges. He always inspired me to not lose sight of the big picture, and pushed me to seek simplicity when solving difficult problems. Dave patiently and tirelessly read all my drafts, sat through every single practice talk, and gave constructive feedback while preserving his great sense of humor. Thank you, Dave, for being such an inspiring advisor.

I wish to thank Dr. Martin Schulz and Dr. Barry Rountree for providing me with the opportunity to intern at Lawrence Livermore National Laboratory and for serving on my committee. Martin always gave insightful comments on research, edited my paper drafts, and taught me how to develop better academic and industrial collaborations. I also know a lot more about beer today than I did before because of Martin.

I remember being stuck with a script problem when I first met Barry at a conference. He helped me by giving me a three-minute bash tutorial, followed by a fifteen-minute introduction to R, further followed by a discussion about his favorite books on evolution. I have learned a lot from my conversations with Barry. His unique way of visualizing data has enabled me to present my research better, and his unconventional approach to problem solving has pushed me to think outside the box.

I would like to thank my committee members, Dr. Saumya Debray and Dr. John Hartman, for their timely feedback and suggestions on my research. I also want to thank Dr. Bronis R. de Supinski for his valuable advice over the years.

I had the opportunity to work with some amazing fellow labmates. Thank you, Gregory Striemer, Peter Bailey, Anjana Sasidharan, Kathleen Shoga, Timothy Meyer, Neha Gholkar, Matthias Maiterth, Joachim Protze and Rogelio Long, for the intense late-night debugging sessions, technical discussions and funny conversations. A special thanks to my friends Saravanakrishnan Krishnamoorthy, Jinyan Guan, Kate Kharitonova, Sabrina Nusrat, Aarthi Goverdhan, Aditi Kapoor, Samitha Manocha, Parul Shukla, and Pratibha Pandey for their support and motivating words.

I also wish to thank Janhavi Sabnis, Akshat Gupta, Saurabh Maniktala, Anisha Goel, Truc Nyugen and Shloka Desai, for being as crazy as me. Thank you for making me laugh hysterically, for cheering me up when things got rough, and for being my family in the US. You all are the best friends anyone could ever ask for. And thank you, Shloka, for help with proofreading this dissertation.

Finally, I want to thank my family for always believing in me and for their unconditional love and support. Thank you, Varsha Patki, for putting up with this younger cousin of yours, and for being there for me. I will always look up to you.

# DEDICATION

To my parents, Anuradha and Arunkumar Patki, for everything. Words can never express how much I love you.

# TABLE OF CONTENTS

| LIST O            | F FIGURES                                                     |  |

|-------------------|---------------------------------------------------------------|--|

| LIST O            | F TABLES                                                      |  |

| ABSTR             | ACT 12                                                        |  |

| СНАРТ             | ER 1 INTRODUCTION                                             |  |

| 1.1               | Hardware Overprovisioning                                     |  |

| 1.2               | Economic Viability of Overprovisioning                        |  |

| 1.3               | Power-Aware Resource Management                               |  |

| 1.4               | Summary of Contributions                                      |  |

| СНАРТ             | ER 2 BACKGROUND                                               |  |

| 2.1               | High Performance Computing (HPC) Basics                       |  |

| 2.2               | Power Basics                                                  |  |

|                   | 2.2.1 Processor Power                                         |  |

|                   | 2.2.2 Power and Energy                                        |  |

| 2.3               | Power Measurement and Control Techniques                      |  |

| 2.0               | 2.3.1 Running Average Power Limit (RAPL)                      |  |

|                   | 2.3.2 IBM BlueGene/Q Environmental Monitor (EMON)             |  |

|                   | 2.3.3 PowerInsight (PI)                                       |  |

|                   | 2.3.4 Limitations                                             |  |

| 2.4               | Basic Economic Terminology                                    |  |

| $\frac{2.1}{2.5}$ | Resource Management Basics                                    |  |

| 2.0               | 2.5.1 Backfilling                                             |  |

|                   | 2.5.2 Simple Linux Utility for Resource Management (SLURM) 34 |  |

| СНАРТ             | ER 3 HARDWARE OVERPROVISIONING                                |  |

| 3.1               | Motivation for Overprovisioning                               |  |

| 3.2               | 1 0                                                           |  |

| 3.3               | Single-Node, Baseline Results                                 |  |

| 3.4               | Multi-node, Overprovisioning Results                          |  |

| 0.1               | 3.4.1 Configurations                                          |  |

| 3.5               | Summary                                                       |  |

# ${\bf TABLE\ OF\ CONTENTS}-Continued$

| СНАРТ | TER 4  | ECONOMIC VIABILITY OF OVERPROVISIONING 53                                                                             |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------|

| 4.1   | Under  | standing Supercomputing Procurement                                                                                   |

| 4.2   |        | e of Overprovisioning                                                                                                 |

| 4.3   | _      | ting the Cost of Overprovisioning                                                                                     |

| 4.4   | -      | Model Formulation and Analysis                                                                                        |

|       | 4.4.1  | Input Parameters: Power Budget and Node Power Values 62                                                               |

|       | 4.4.2  | Input Parameter: Effective Cost Ratio                                                                                 |

|       | 4.4.3  | Input Parameters: Performance Parameter and Workload                                                                  |

|       |        | Scalability Model                                                                                                     |

|       | 4.4.4  | Model Formulation                                                                                                     |

|       | 4.4.5  | Analysis                                                                                                              |

| 4.5   | Summ   | ary                                                                                                                   |

| СНАРТ | TER 5  | RESOURCE MANAGER FOR POWER                                                                                            |

| 5.1   | Design | ing Power-Aware Schedulers                                                                                            |

| 5.2   | Schedu | ıling Policies                                                                                                        |

|       | 5.2.1  | The Traditional Policy                                                                                                |

|       | 5.2.2  | The <i>Naive</i> policy                                                                                               |

|       | 5.2.3  | The Adaptive policy                                                                                                   |

|       | 5.2.4  | Example of Policies                                                                                                   |

| 5.3   | Impler | mentation                                                                                                             |

| 5.4   | Predic | ting Performance and Power                                                                                            |

|       | 5.4.1  | Dataset                                                                                                               |

|       | 5.4.2  | Model                                                                                                                 |

| 5.5   | Experi | imental Details                                                                                                       |

| 5.6   | Result | $s \dots \dots$ |

|       | 5.6.1  | Model Evaluation Results                                                                                              |

|       | 5.6.2  | Analyzing Scheduling Policies                                                                                         |

|       | 5.6.3  | Analyzing Altruistic User Behavior                                                                                    |

|       | 5.6.4  | Power Utilization                                                                                                     |

| 5.7   | Summ   | ary 102                                                                                                               |

| СНАРТ |        | RELATED WORK                                                                                                          |

| 6.1   | Energy | y, Power and Performance Research                                                                                     |

|       | 6.1.1  | Energy-Efficient HPC                                                                                                  |

|       | 6.1.2  | Power-Constrained HPC                                                                                                 |

| 6.2   | Power- | -Aware Scheduling Research in HPC                                                                                     |

# ${\bf TABLE\ OF\ CONTENTS}-Continued$

| СНАРТ | TER 7  | CONCLUSIONS AND FUTURE WORK                               | 110 |

|-------|--------|-----------------------------------------------------------|-----|

| 7.1   | Hardw  | are Overprovisioning Summary                              | 110 |

| 7.2   | Power- | Aware Resource Management Summary                         | 111 |

| 7.3   | Future | Work                                                      | 112 |

|       | 7.3.1  | Impact of Manufacturing Variability                       | 112 |

|       | 7.3.2  | Understanding Impact of Temperature on Power, Performance |     |

|       |        | and Resilience                                            | 115 |

|       | 7.3.3  | Dynamic Reconfiguration in Overprovisioning               | 117 |

|       | 7.3.4  | Self-tuning Resource Managers                             | 118 |

|       |        |                                                           |     |

# LIST OF FIGURES

| 1.1<br>1.2                      | Power Consumption on Vulcan                         |

|---------------------------------|-----------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Typical HPC System                                  |

| 3.1<br>3.2<br>3.3               | Average PKG and DRAM Power Consumption Per Socket   |

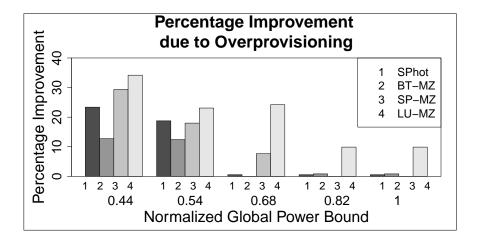

| 3.4                             | Performance Improvement due to Overprovisioning     |

| 3.5                             | Detailed Overprovisioning Results                   |

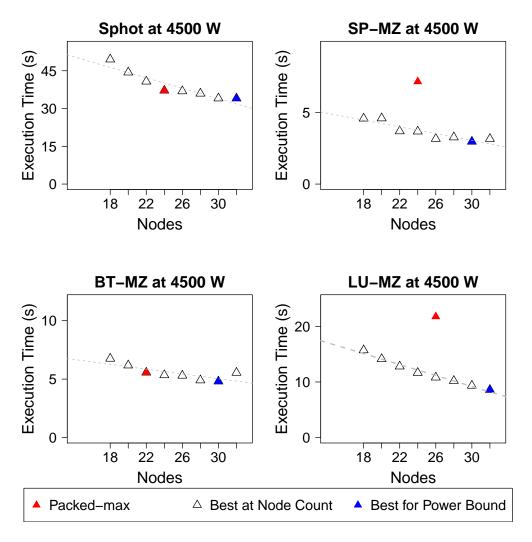

| 3.6                             | Example of SP-MZ at 4500 W                          |

| 3.7                             | Configurations for SPhot and LU-MZ on a Single Node |

| 4.1                             | Benefits of Adding More Nodes, 3500 W               |

| 4.2                             | Benefits of Adding More Nodes, 4500 W               |

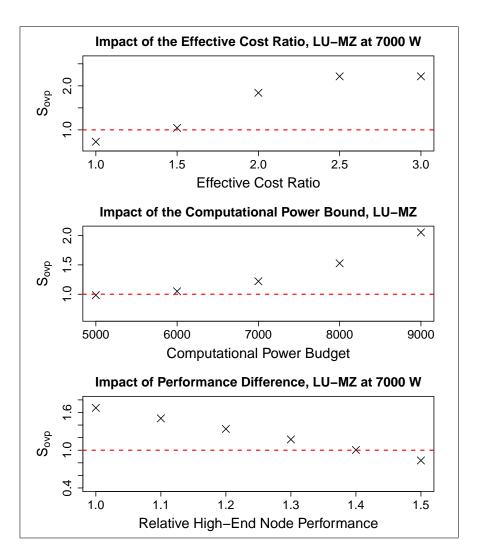

| 4.3                             | LU-MZ Analysis                                      |

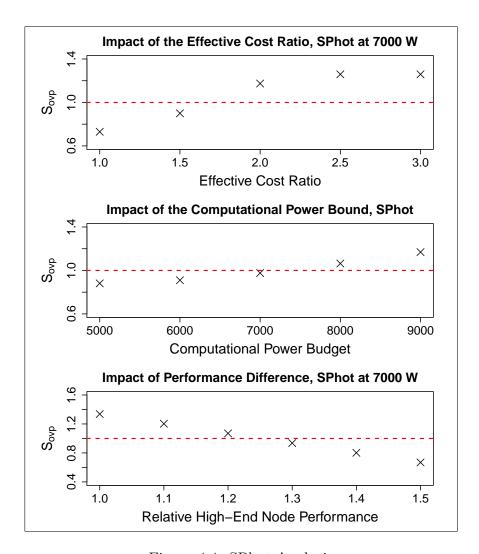

| 4.4                             | SPhot Analysis                                      |

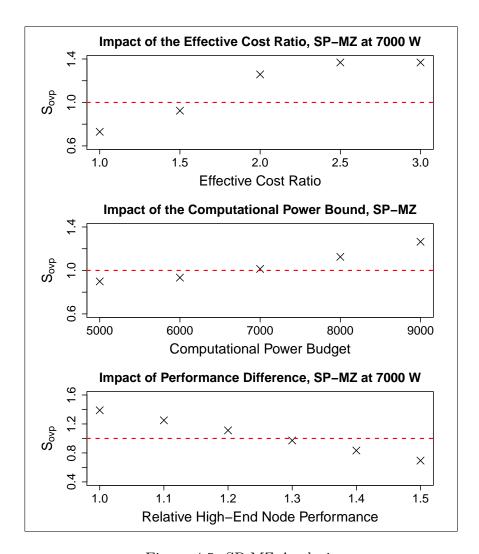

| 4.5                             | SP-MZ Analysis                                      |

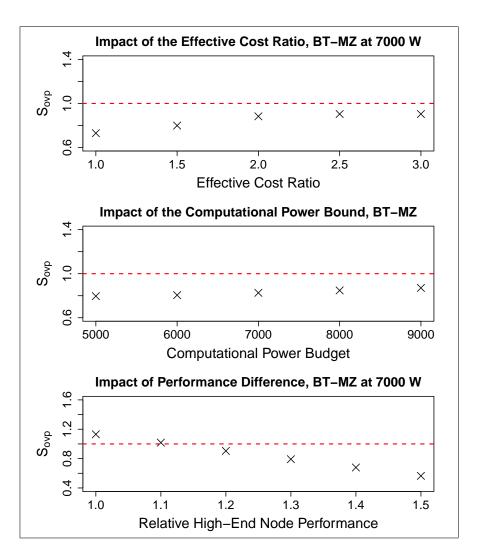

| 4.6                             | BT-MZ Analysis                                      |

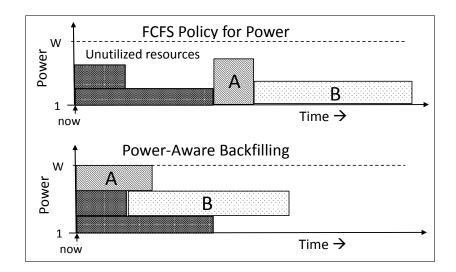

| 5.1                             | Advantage of Power-Aware Backfilling                |

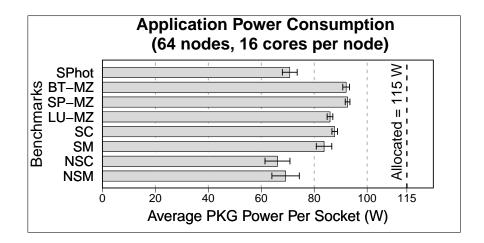

| 5.2                             | Application Power Consumption                       |

| 5.3                             | Performance with Overprovisioning                   |

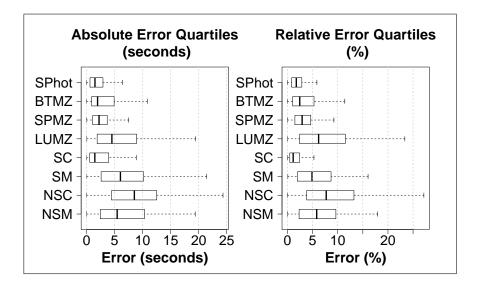

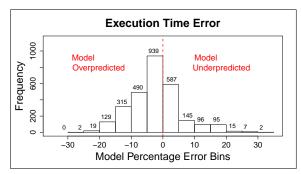

| 5.4                             | Error Quartiles of Regression Model                 |

| 5.5                             | Range of Prediction Errors                          |

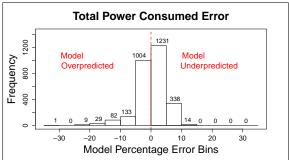

| 5.6                             | Model Results on the Random Trace                   |

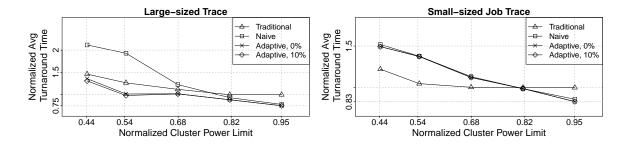

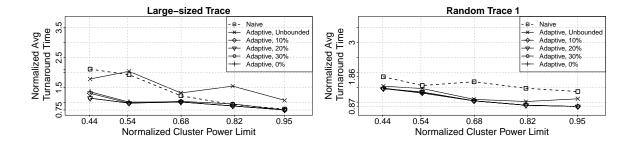

| 5.7                             | Results for Large-sized Jobs                        |

| 5.8                             | Results for Small-sized Jobs                        |

| 5.9                             | The Adaptive Policy with Varying Thresholds         |

|                                 | Benefits for Altruistic User Behavior               |

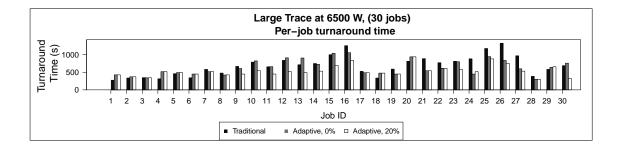

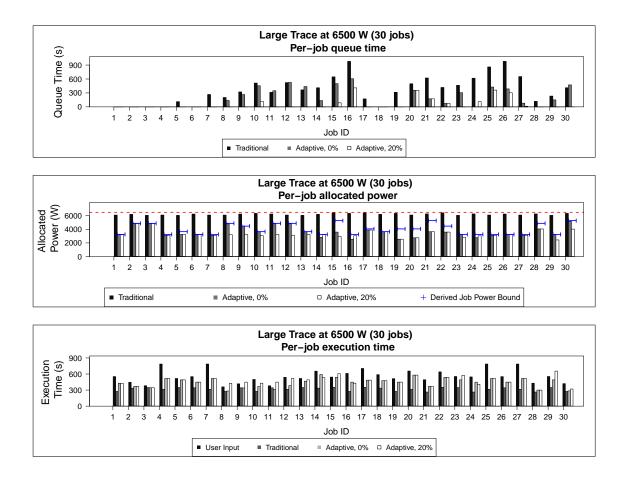

| 5.11                            | Detailed Results for the Large Trace at 6500 W      |

| 5.12                            | Timeline of Scheduling decisions                    |

# LIST OF FIGURES – Continued

| 5.13 | Utilizing Power Efficiently                                   | 101 |

|------|---------------------------------------------------------------|-----|

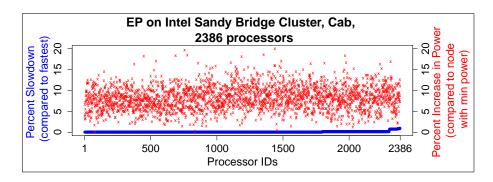

| 7.1  | Performance and Power on Cab, LLNL                            | 113 |

| 7.2  | Variation in Performance Under a Power Constraint on Cab      | 115 |

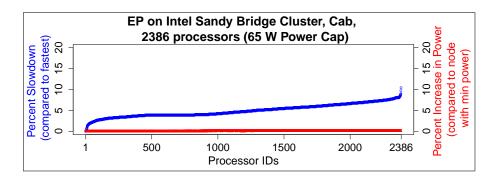

| 7.3  | Impact on Ambient Air Temperature on High-Performance Linpack | 116 |

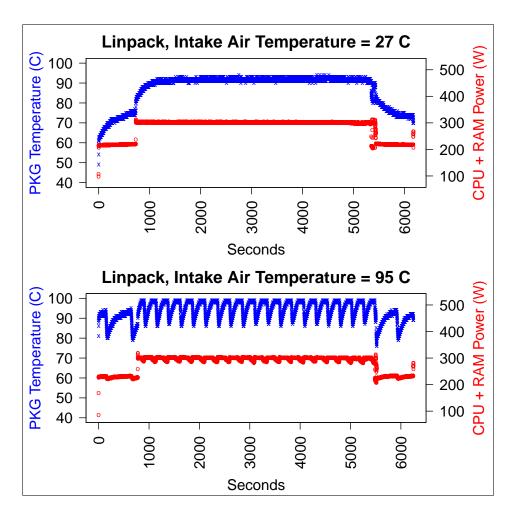

| 7.4  | Performance and Temperature on Cab                            | 116 |

# LIST OF TABLES

| 2.1 | Power Measurement Techniques                       | 28 |

|-----|----------------------------------------------------|----|

| 4.1 | Cost of a DOE HPC System (Source: Magellan Report) | 54 |

| 4.2 | Power and Performance Data, 3500 W                 | 59 |

| 4.3 | Comparing 32nm and 22nm processor technologies     | 61 |

| 4.4 | Model Input Parameters                             | 63 |

| 4.5 | IDs used in Model Formulation                      | 67 |

| 4.6 | Model Output Parameters                            | 68 |

| 4.7 | Example: Default Input Parameters                  | 70 |

| 4.8 | Example: Workload Scalability Model Parameters     | 70 |

| 4.9 | Example: Intermediate and Output Values            | 71 |

| 5.1 | RMAP Job Scheduling Policies                       | 82 |

| 5.2 | List of Configurations for SP-MZ                   | 85 |

| 5.3 | Schema for Job Details Table                       | 87 |

| 5.4 | Average Turnaround Times                           | 98 |

#### ABSTRACT

Power management is one of the most critical challenges on the path to exascale supercomputing. High Performance Computing (HPC) centers today are designed to be worst-case power provisioned, leading to two main problems: limited application performance and under-utilization of procured power. In this dissertation we introduce hardware overprovisioning: a novel, flexible design methodology for future HPC systems that addresses the aforementioned problems and leads to significant improvements in application and system performance under a power constraint.

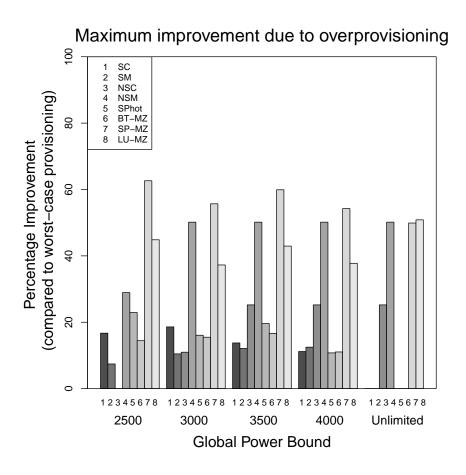

We first establish that choosing the right configuration based on application characteristics when using hardware overprovisioning can improve application performance under a power constraint by up to 62%. We conduct a detailed analysis of the infrastructure costs associated with hardware overprovisioning and show that it is an economically viable supercomputing design approach. We then develop RMAP (Resource MAnager for Power), a power-aware, low-overhead, scalable resource manager for future hardware overprovisioned HPC systems. RMAP addresses the issue of under-utilized power by using power-aware backfilling and improves job turnaround times by up to 31%. This dissertation opens up several new avenues for research in power-constrained supercomputing as we venture toward exascale, and we conclude by enumerating these.

#### CHAPTER 1

#### INTRODUCTION

As of June 2015, the world's fastest supercomputer, Tianhe-2, delivers 33.8 petaflops<sup>1</sup> of sustained performance while using 17.6 MW of power. As we push the boundaries of supercomputing further, power becomes a limiting and expensive resource. Effectively translating this limited power resource into performance and utilizing it fully are thus critical challenges in the next generation of supercomputing. The U.S. Department of Energy has set an ambitious target of achieving an exaflop<sup>2</sup> under a constraint of 20 MW by 2023 (Department of Energy, 2014)—thus requiring a 30-fold improvement in performance with merely 14% increase in power and rendering existing approaches obsolete. This has triggered research both in the semiconductor industry and the supercomputing community, with the former focusing on designing efficient processor, memory and network technologies, and the latter focusing on utilizing this new hardware and developing better system software to manage power and improve performance while ensuring reliable operation. Both these directions for research are complementary and are essential in order to achieve exascale.

The focus of the research conducted in this dissertation is to optimize application as well as system performance in power-constrained supercomputing. The key contributions include the idea of hardware overprovisioning and the design and implementation of associated system software necessary to realize its benefits in supercomputing. Hardware overprovisioning is a novel technique that improves performance significantly under an application-level power bound. We study its performance benefits and analyze its economic viability so as to understand the associated tradeoffs. We also present RMAP (Resource MAnager for Power), a resource manager targeted at future hardware overprovisioned and power-limited systems. We

<sup>&</sup>lt;sup>1</sup>A supercomputer that can perform 10<sup>15</sup> floating point operations per second

<sup>&</sup>lt;sup>2</sup>Or, 10<sup>18</sup> floating point operations per second

analyze how RMAP can be deployed on a real system with multiple users and show how it can improve system throughput and power utilization. The following subsections provide an overview of the contributions of this dissertation.

## 1.1 Hardware Overprovisioning

Supercomputers today are designed to be worst-case power provisioned, implying that all nodes in the system can run at peak power simultaneously. While this power allocation strategy is useful for a few power-hungry benchmarks such as High-Performance Linpack, it leads to inefficient use of power for most HPC production applications that fail to utilize the allocated peak power on a node.

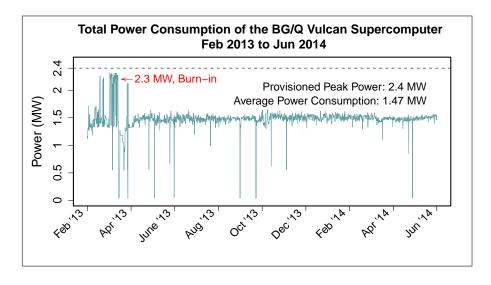

Figure 1.1: Power Consumption on Vulcan

One of the key limitations of worst-case provisioning in supercomputing design is underutilization of the power infrastructure. An example of this can be found in data collected on Vulcan (see Figure 1.1), which is a BlueGene/Q system located at Lawrence Livermore National Laboratory (LLNL). As of June 2015, Vulcan is the tenth-fastest supercomputer in the world with 393,216 compute cores and has been provisioned with 2.4 MW of power. Power consumption data was gathered from Vulcan every three minutes by LLNL's Livermore Computing division for over 16 months. This data

shows that applications used only 1.47 MW on average, with the only exception being the burn-in phase. This under-utilization of power has many negative ramifications, such as the use of lower water temperatures than needed for cooling—which leads to additional power wasted on water chillers.

Ideally, supercomputing centers should utilize the procured power fully to accomplish more science, especially because power is a limited and expensive resource. Thus, a more flexible and efficient design approach is to build a reconfigurable system that has more capacity (nodes) under the same site-level power constraint and can adapt to requirements of the applications. Such a system can provide limited power to a large number of nodes, peak power to a smaller number of nodes, or use an alternative allocation in between based on application characteristics. This approach is referred to as hardware overprovisioning (or overprovisioning for short).

Good performance on an overprovisioned system relies on choosing a configuration that takes the application's characteristics into consideration. We define a configuration as a tuple consisting of three values—number of nodes, number of cores per node, and power bound per node. Our research demonstrates that choosing the right configuration on an overprovisioned system can reduce individual application execution time under a power bound by up to 62% and by 32% on average when compared to worst-case provisioning (Patki et al., 2013), thus improving performance by 2.63x (1.47x on average). For example, for applications that are highly scalable, running more nodes at lower power per node might result in shorter execution times for the same amount of power. Similarly, for applications that are memory-bound, running fewer cores per node may result in the best performance.

# 1.2 Economic Viability of Overprovisioning

An overprovisioned system has more capacity than it can simultaneously fully power. Such a system can provide significant performance improvements in power-constrained scenarios. However, these benefits come with an additional hardware and infrastructure cost, and it is essential to conduct a thorough cost-benefit analysis before investing in

large-scale overprovisioned systems. The hardware cost for an overprovisioned system depends on several factors, such as the cost of the underlying processor architecture and the high-speed interconnection network. A hardware cost budget thus provides a choice between purchasing fewer, high-end processors that result in a worst-case provisioned system, or more low-cost, previous generation processors that can be overprovisioned. We develop a model to compare the costs and benefits of worst-case provisioning with overprovisioning, thus providing an analytical tool for future HPC system designers. We show that it is possible to achieve better performance with overprovisioned systems while keeping the system acquisition cost constant.

#### 1.3 Power-Aware Resource Management

For overprovisioning to be practical, system software such as resource managers and runtime systems need to be made power-conscious. With this goal in mind, we developed RMAP (Resource MAnager for Power) (Patki et al., 2015), a low-overhead, scalable resource manager targeted at future power-constrained systems. Similar to existing schedulers, users request a node count and time limit for their job. Traditional resource managers use this information to determine a physical node allocation for the job based on a scheduling policy. Jobs have to wait in the job queue until enough nodes are available, and are terminated if they exceed their requested time limit. The traditional assumption is that the job will be allocated all the power (and cores) on the requested nodes.

Future power-limited systems, however, will have to enforce job-level and node-level power bounds. In order to address this, RMAP translates the user's node request to a job-level power bound in a fair-share manner by allocating the job power proportional to the fraction of nodes of the total system that it requested. Within RMAP, we propose and implement an adaptive policy based on overprovisioning and power-aware backfilling. The main goals for this policy are to improve application performance as well as system power utilization while adhering to the derived job-level power bound. Additionally, the policy also strives to minimize the average turnaround time for all

jobs in the job queue. Power-aware backfilling is a simple, greedy algorithm that trades some of the performance benefits (raw execution time) obtained from overprovisioning for faster turnaround times and shorter queue wait times. Additionally, two other baseline policies that represent naive overprovisioning and worst-case provisioning are implemented within RMAP. The naive overprovisioning policy finds the best performing configuration under the derived job-level power bound; and the policy based on worst-case provisioning guarantees safe, correct execution by allocating the requested nodes at peak power to the job while adhering to the power constraint.

We implement RMAP by extending SLURM, a popular, open-source HPC resource manager that is deployed on several of the Top500 supercomputers (Yoo et al., 2003). Our results indicate that the adaptive policy can increase system power utilization while adhering to strict job-level power bounds and can lead to 31% (19% on average) and 54% (36% on average) faster average job turnaround times when compared to the policies based on worst-case provisioning and naive overprovisioning, respectively (Patki et al., 2015). It is important to note that naive overprovisioning may result in worse turnaround times, and that future supercomputing system software needs to be intelligent and adaptive.

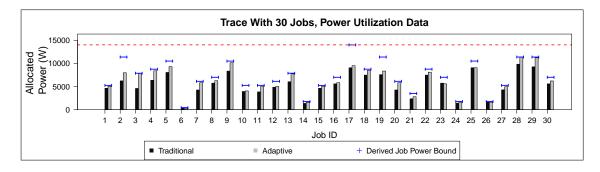

Figure 1.2: Power Utilization

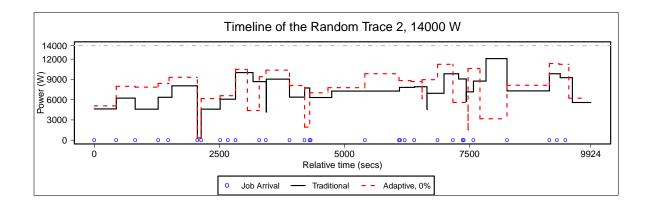

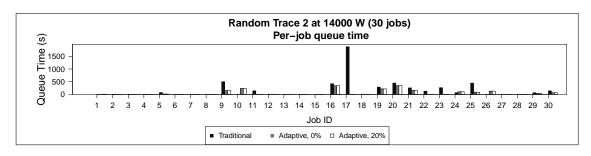

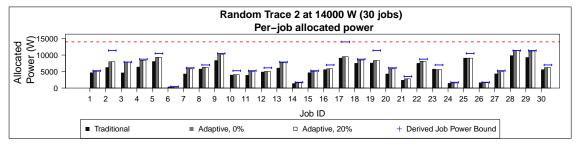

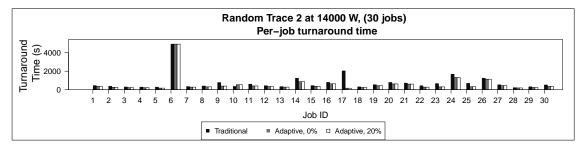

Figure 1.2 depicts power results of the adaptive and traditional policies within RMAP on a random job trace in a scenario with unconstrained power (14,800 W on a 64-node system, represented by a dashed red line). The y-axis is the power allocated to the job for execution, the x-axis represents the Job IDs, and the blue lines on the

top indicate the derived job-level power bound using fair-share. As can be observed from this graph, the adaptive policy always utilizes power better than the traditional policy. For some jobs, such as Job 3, the adaptive policy utilizes 70% more power than the traditional policy. Overall, the adaptive policy utilizes 17% more per-job power, leading to significantly less wasted power and faster turnaround times.

### 1.4 Summary of Contributions

In summary, this dissertation makes the following contributions:

- We introduce hardware overprovisioning and show that it can improve performance under an application-level power bound by up to 62% (32% on average).

- We present a detailed study on the cost-benefit analysis of hardware overprovisioning and develop a model that HPC system designers can use to determine whether overprovisioning results in a net benefit for their site.

- We describe RMAP, a resource manager targeted at future power-limited systems. Within RMAP, we design the *Adaptive* policy which uses hardware overprovisioning and power-aware backfilling. We show that this novel policy results in up to 31% (19% on average) faster turnaround times for a job queue when compared to a simple, traditional policy based on worst-case provisioning, and that it also improves overall system power utilization.

The rest of this dissertation is organized as follows. Background information about power management and scheduling in high-performance computing systems is provided in Chapter 2. Chapter 3 introduces hardware overprovisioning and highlights its benefits. Chapter 4 analyzes the economic viability of hardware overprovisioned supercomputers. Chapter 5 introduces RMAP (Resource MAnager for Power), which is a job scheduling system targeted toward future power-limited supercomputers. Chapter 6 presents related work in the area, and finally, Chapter 7 concludes this dissertation and describes future research.

#### CHAPTER 2

#### BACKGROUND

In this chapter, we present background information about power, scheduling and economic terminology used in the context of supercomputing. Section 2.1 provides an overview of the organization of large-scale HPC facilities. Sections 2.2 and 2.3 focus on processor power measurement and management techniques. Section 2.4 introduces economic terms that are used in Chapter 4. Section 2.5 discusses backfilling, a common job scheduling technique used to improve system utilization in current supercomputing systems.

## 2.1 High Performance Computing (HPC) Basics

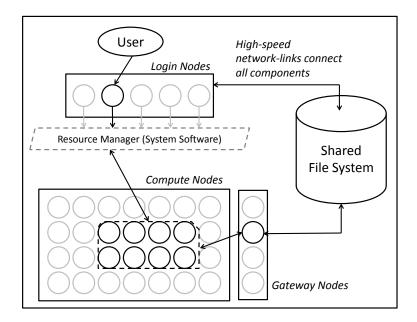

A high-performance computing facility consists of parallel computing systems with several thousand nodes linked together to provide high computational capacity in order to solve some of the most pressing problems in science and engineering. A typical system is laid out as a combination of login, compute and gateway nodes. Login nodes generally provide access to the main system and are shared by multiple users. They are interactive and can be used for tasks such as compiling applications, submitting job requests, launching GUI interfaces and sometimes debugging. Only a small percentage of the system is comprised of login nodes. Users log in to the HPC system with these nodes and submit requests to access compute nodes. These requests are granted by system resource managers.

Compute nodes determine the computational strength of an HPC system and are used to run critical applications. In general, compute nodes are not shared and are not interactive. Users request a set of compute nodes to execute their applications with the help of a resource management system (such as SLURM, discussed in Section 2.5.2). Compute nodes typically consist of multiple sockets (each with multiple cores)

Figure 2.1: Typical HPC System

and associated memory. They may also have additional processing components or accelerators, such as General Purpose Graphics Processing Units (GPGPUs) or Xeon Phis. Login nodes and compute nodes may have similar architectures.

Compute nodes are organized in racks and are connected with other compute nodes as well as other components of the HPC system with the help of a high-speed interconnect (typically InfiniBand). The layout of the underlying network topology (mesh, tree, or torus) usually determines the layout of the compute nodes in the HPC system. HPC compute nodes are usually diskless and do not have local storage. They are connected to persistent storage servers with the help of gateway nodes. Storage servers host parallel file systems, which provide fast, high-bandwidth access and are also fault-tolerant. An example of such a file system is Lustre (Koeninger, 2003). Figure 2.1 shows this layout and also depicts how a user interacts with a typical HPC system.

HPC applications can be *strongly-scaled* or *weakly-scaled*. For strong scaling, the total input problem size stays fixed as more compute nodes are added to the application. In the case of weak scaling, the problem size per node stays constant. Thus, when more nodes are added, the total input problem size changes.

#### 2.2 Power Basics

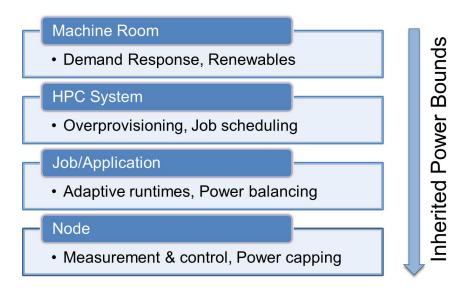

A typical supercomputing site is organized in a hierarchical manner. Each site has a few machine rooms, and each machine room hosts a few HPC systems. Each of these HPC systems have various components as described in Section 2.1. In the future, power-constrained supercomputing facilities will have to enforce power bounds at each level in the aforementioned hierarchy to ensure reliable operation. Site-level power constraints will apply across multiple machine rooms. Electricity service providers as well as the infrastructure availability at the facility will determine the amount of power that can be brought into each machine room. These machine-room level power bounds will then be translated to system-level power bounds. Each HPC system will have its own power bound, so that all these systems can function effectively and simultaneously within the power budget of the machine room. These system-level power bounds will further be inherited by jobs and applications, which in turn will translate to component (or node) level power bounds. Most of these power bounds, including the site-level constraints will be dynamic owing to different sources of energy generation (Bates et al., 2015).

Figure 2.2 shows these inherited power bounds. Techniques such as hardware overprovisioning and power-aware job scheduling, which are the focus of this dissertation, will be used at the system-level. Additionally, runtime systems will need to balance power (in addition to load-balancing) and improve performance at the application-level. These steps can be accomplished by using node-level power measurement and management techniques that are typically supported by the underlying hardware.

#### 2.2.1 Processor Power

All the components described in Section 2.1 (nodes, interconnects, storage servers etc.) contribute to the total power draw of an HPC system, which has two key components: base power and dynamic power. Base power (sometimes referred to as idle or static power) is the amount of power required to operate the HPC system without an active

Figure 2.2: Inherited Power Bounds

workload (that is, no jobs are running and the system is idle). It is thus the minimum amount of power that the HPC facility needs to be able turn on all the components in the system and leave them in idle state. This typically includes the storage server and interconnect power and the power consumed by the nodes when they are inactive. Dynamic power, on the other hand, depends on the workload or application. The main contributors to dynamic power are nodes that are executing active applications (thus their CPU(s) and memory are in use).

Traditionally, HPC systems are designed to be worst-case power provisioned. Worst-case provisioned systems are designed to account for the maximum possible power consumption. Node components (CPU and memory) typically have a vendor-specified Thermal Design Point (TDP) that indicates the maximum power draw associated with the component. The maximum power consumption for an HPC system can thus be determined by the sum of the TDPs of all the nodes and other system power (such as disks and interconnects). In reality, though, nodes rarely reach their TDP limits when running real applications. Allocating all the power on a node to an application is thus unnecessary.

In order to minimize the wastage of procured power (refer to Figure 1.1 from Chapter 1), it is critical to understand the power profiles of scientific applications and their contributions to dynamic power. The focus of this dissertation is thus on CPU and memory power consumption. In general, CPU power consists of the power for cores and for on-chip caches and depends on the operating frequency of the processor (Mudge, 2001). More specifically, CPU power can be defined as shown in Equation 2.1 and has three parts. Dynamic or switching power,  $P_{dyn}$ , is associated with charging and discharging of capacitance and corresponds to switching from a 0 to 1 and vice versa. Short-circuit power, or  $P_{sc}$ , is a small amount of power that is consumed during brief, momentary transitions. Finally, leakage power, or  $P_{leak}$ , is the power lost due to transistor leakage current. In current circuits, the main component is  $P_{dyn}$ , which depends on the frequency of operation, f, and the supply voltage,  $V_{dd}$ , as shown in Equation 2.2.

$$P_{cpu} = P_{dyn} + P_{sc} + P_{leak} \tag{2.1}$$

$$P_{dyn} = CV_{dd}^2 f (2.2)$$

Thus, power consumption in processors is controlled by changing the frequency of operation or by scaling the supply voltage. Doing so during the execution of a user application is commonly referred to as Dynamic Voltage and Frequency Scaling (DVFS). DVFS has been widely applied to power and energy research in HPC (Cameron et al., 2005; Hsu and Feng, 2005; Springer et al., 2006; Ge et al., 2007; Li and Martìnez, 2006; Li et al., 2004; Ge et al., 2007; Kappiah et al., 2005; Rountree et al., 2007, 2009). Memory power consumption also depends on the operating frequency of the associated DRAM (David et al., 2010). Techniques such as DVFS, however, are not available for current memory technologies due to the volatile nature of random-access memories (Mittal, 2012).

# 2.2.2 Power and Energy

Research in power-constrained supercomputing is often confused with energy efficiency research for data centers. It is important to thus clarify the difference between the two. The main goal for HPC centers is to accomplish useful science. This can be realized by utilizing all the procured power efficiently and by translating it into application performance and system throughput. Saving energy or power is typically considered secondary as long as a site-wide power constraint is met. HPC facilities also have symbiotic contractual relationships with their electricity providers that support these goals.

For data centers, on the other hand, the focus typically is to meet a service-level agreement. Performance can be compromised in order to minimize the operating cost as long as the desired service level is met. Thus saving energy and reducing electricity utility bills at the cost of reduced application performance is a viable option for data centers.

Saving energy for HPC systems subject to a small, acceptable delay has already been studied widely (Cameron et al., 2005; Hsu and Feng, 2005; Springer et al., 2006; Ge et al., 2007; Li and Martìnez, 2006; Li et al., 2004; Ge et al., 2007; Kappiah et al., 2005; Springer et al., 2006). It has however been demonstrated that it is possible to achieve significant energy savings without incurring any performance penalties in HPC systems (Rountree et al., 2007, 2009). As a result, the goal for future HPC system designers is to maximize performance under a power constraint.

#### 2.3 Power Measurement and Control Techniques

Several vendor-specific and agnostic mechanisms to measure and manage node power have been developed. Some of these mechanisms use sensors and some others use performance counter based models to estimate component power. The techniques used in this dissertation include Intel's Running Average Power Limit (RAPL), Penguin Computing's PowerInsight (PI) and IBM's Environmental Monitor (EMON). We discuss these techniques in detail below. Of these three, RAPL is the only technique that

allows us to constrain and manage power at present. It is expected that more systems will provide such capabilities in the future. Table 2.1 summarizes these techniques and shows the granularity of measurement available in each case. For most of our work, we use RAPL, with the exception of the processor manufacturing variability study presented in Chapter 7. We primarily focus on module power (CPU sockets and DRAM) in this work, mostly because it can be controlled dynamically in HPC systems and can be used to constrain and manage power at a fine granularity. Other components, such as interconnects, do not provide this dynamic control and account for static or base power consumption.

## 2.3.1 Running Average Power Limit (RAPL)

RAPL is a power management interface that has been introduced with the Intel Sandy Bridge microarchitecture (Intel, 2011; David et al., 2010). It supports on-board power measurement and hardware power capping across two main domains—Package (PKG or CPU) and Memory (DRAM). The PKG domain represents the processor die (cores and on-chip caches), and the DRAM domain includes directly attached memory. Additionally, power measurement is supported across the Power Plane 0 (PP0) and Power Plane 1 (PP1) domains. PP0 covers mostly the cores, while PP1 covers so-called uncore devices (for example, the off-chip last-level cache, the Intel QuickPath Interconnect or an integrated graphics card). For the Intel Sandy Bridge microarchitecture, there are two processor models, the client (family: 0x06, model: 0x2A) and the server (family: 0x06, model: 0x2D). The client model supports the PKG, PP0 and DRAM domains. We use the Sandy Bridge server model in our work.

The interface to RAPL is implemented with the help of programmable Machine Specific Registers (MSRs). To access these MSRs, developers can use the Linux msr kernel module. This kernel module exports a file interface at /dev/cpu/N/msr that can be used to read from or write to the MSRs given appropriate permissions using the rdmsr and wrmsr instructions. Note that rdmsr and wrmsr are privileged instructions that have to execute from within the kernel space on protection ring 0. Each RAPL

domain has a 32-bit, read-only ENERGY\_STATUS MSR for measurement, which is updated approximately every millisecond. This MSR is expected to roll over within hours owing to the precision of the unit used (joules). Average power is calculated by using this MSR and by dividing the accumulated joules by elapsed time.

RAPL also supports power capping across the PKG and DRAM domains. To enforce a power cap using RAPL, users can specify a power bound and a time window in the POWER\_LIMIT MSR, and the hardware ensures that the average power over the time window does not exceed the specified bound in the requested power domain. The POWER\_INFO set of registers provides information on the thermal specification power, the lowest power bound and the largest time window supported. For the Sandy Bridge server model, the lowest PKG power bound is 51 W, the thermal specification is 115 W, the largest possible time window is 20 seconds, and the maximum power rating is 180 W. Additionally, the RAPL interface includes the MSR\_RAPL\_POWER\_UNIT read-only register that lists the units for power, energy and time in Watts, Joules and Seconds respectively, at architecture-specific precision. The Sandy Bridge server model has units of 0.125W, 0.0000152J and 0.000977 seconds. DRAM power capping is often not supported in mainstream processors and is considered a test feature. Techniques other than DVFS, such as controlling the burstiness and flow of memory traffic, are used to control DRAM power with RAPL.

Intel also has a Turbo Boost feature, which accelerates processor performance dynamically by allowing cores to run faster than the rated operating frequency in some scenarios. Whether Turbo Boost will be used depends on the workload and the ambient temperature. An MSR can be used to enable or disable the Turbo mode, but the operating frequency of the processor in the Turbo mode cannot be directly controlled in software. While the maximum Turbo frequency can be set in software, the actual frequencies of operation are determined at runtime.

To facilitate power measurement of HPC applications, we developed the *librapl* library to ensure safe user-space access of Intel's RAPL MSRs. This library uses the MPI profiling interface to intercept MPI\_Init() and MPI\_Finalize() calls to set up the necessary MSRs. Thus, we do not have to modify application source code to measure

or cap power. The library can also sample MPI programs at a desired time interval and intercept every MPI call in the application to gather timing and energy/power information. It further infers the operating frequency for each core using the APERF and MPERF MSRs (Intel, 2011). Our library can be downloaded from https://github.com/tpatki/librapl. A modified version of this library with an improved interface has been recently released by Lawrence Livermore National Laboratory (Shoga et al., 2014) in production form (now referred to as libmsr).

## 2.3.2 IBM BlueGene/Q Environmental Monitor (EMON)

BlueGene is an IBM project for designing power-efficient petaflop supercomputers. Three system architectures—BlueGene/L, BlueGene/P, and BlueGene/Q—have been designed in this project. BlueGene/Q (BG/Q) is the third (and current) generation in the BlueGene series of supercomputers. Each rack of a BG/Q machine houses two midplanes, eight link cards, and two service cards. Each midplane has 16 node boards, each of which has 32 compute cards (nodes) connected by a 5D-torus. Power measurement is supported at the node board level. A compute card has 17 active cores, 16 of which are application cores. The 17th core is used for system software. There is an additional 18th core that has been deactivated and is only used to increase manufacturing yield. Measurements are supported across seven different domains, the main ones being chip cores (CPU) and chip memory. Other domains include HSS network transceiver and compute/link chip, Chip SRAM, Optics, Optics/PCIExpress and Link chip core.

To facilitate power measurement, each node board is connected to an FPGA over the EMON bus, which in turn is connected to two Direct-Current Assemblies (DCAs). The DCAs have a microcontroller that periodically calculates instantaneous power (Wallace et al., 2013a,b; Yoshii et al., 2012) and communicates with the FPGA over the I2C bus. The FPGA can relay data to the BG/Q compute nodes over the EMON bus. IBM provides an EMON API to access power consumption data.

Technique Granularity Power Reported Capping RAPL Yes Average  $1 \, \mathrm{ms}$ PowerInsight Instantaneous 1 ms (or less) No **BGQ EMON** Instantaneous 300 msNo

Table 2.1: Power Measurement Techniques

## 2.3.3 PowerInsight (PI)

PI is an architecture-independent, sensor-based technique to monitor node power (DeBonis et al., 2012; Laros et al., 2013). The PI architecture consists of three components: (1) a harness with sensor modules for measurement; (2) a cape, or carrier board, with three Analog-to-Digital-Converters (ADC) connected to the sensor modules, and; (3) a BeagleBone core with an ARM Cortex A8 processor, 256 MB of memory, and USB/Ethernet connectivity to the primary node being measured.

Each sensor module is an Allegro ACS713 Hall Effect current sensor and a voltage divider. Typically, the BeagleBone is plugged in to the motherboard using the USB port which provides console connectivity to the node. CPU and DRAM power consumption data can be measured by using the *getRawPower* software utility or with the provided PI-API.

#### 2.3.4 Limitations

At present, a general standard for measuring and managing power does not exist. The Energy Efficient High Performance Computing Working Group (EE HPC WG) has started working towards this goal recently (EE HPC WG, 2014). Current vendor-specific techniques, such as Intel's RAPL, are targeted at certain specific architectures and are not portable. While PI is an architecture-independent mechanism, it has not been studied widely yet and is difficult to deploy at scale.

Another key concern with current measurement and control techniques is their accuracy. Model-based techniques (such as RAPL on the Sandy Bridge

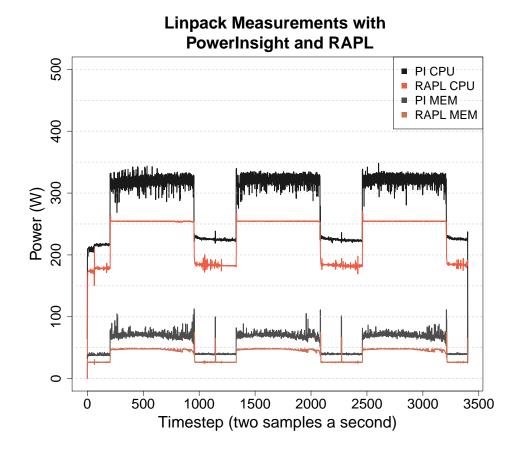

Figure 2.3: Comparison of RAPL and PI on High-Performance Linpack

micro-architecture) are subject to prediction errors, but these error margins are not publicly available. The general agreement in the community is that the error is under 10% (Rotem et al., 2012). Sensor-based and power meter-based measurements are also subject to errors and need to be analyzed carefully. For some measurements, it can be unclear as to what exactly is being measured. An example of this can be seen in Figure 2.3. This figure depicts power measurements using RAPL and PI when High-Performance Linpack was running on a 24-core Ivy Bridge node. As discussed earlier, RAPL and PI have similar granularity of measurement (about 1 ms). RAPL reports average power over the 1 ms time window, and PI reports instantaneous power. In the figure, we show power measurements reported by RAPL and PI for both CPU and memory. As can be observed, these measurements do not coincide and there is a

wide gap in the reported data. One explanation for this gap from Intel is that the PI sensors are measuring the voltage regulator power in addition to the component power. This hypothesis, however, has not been tested yet. It is thus critical to understand what is being measured in each case, how this measured information is being reported, and what the error bounds are. In this dissertation, we use Intel's RAPL, primarily because it gives us the ability to control and cap power.

#### 2.4 Basic Economic Terminology

For any HPC system, two main expenditures need to be considered for procurement—capital expenditures (or, CapEx) and operational expenditures (or, OpEx). CapEx refer to initial investment costs that are made upfront. For example, the purchasing cost of servers or the construction cost of the machine room (including space and cooling infrastructure). These costs depreciate over time. OpEx, on the other hand, represent recurring costs that are necessary to successfully run the HPC system. These may include maintenance and support costs for the hardware, repair costs for any failed components, electricity costs and human resources costs. Power is a critical component of both CapEx and OpEx. With power, we need to include hardware costs, conditioning and delivery costs, electricity costs and cooling costs. HPC system procurement costs are typically business sensitive and limited information is available in the public domain. The Magellan Report provides information for the Hopper supercomputer (Department of Energy, 2011), and we discuss this in Chapter 4.

### 2.5 Resource Management Basics

On a traditional HPC system, users submit jobs by specifying a node count and an estimated runtime. These resource requests are maintained in a *job queue*, and users are allocated dedicated nodes based on a scheduling policy. The job executes when the resource manager acquires the specified number of nodes. If the job exceeds the estimated runtime, it is terminated. Depending on the size (node count) of their request, most HPC users are required to use specific partitions within the system. For example,

most high-end clusters have a *small* debug partition that specifically targets small-sized jobs and a general-purpose *batch* partition for medium and large-sized jobs.

One example of a scheduling policy is First-Come First-Serve (FCFS), which is non-preemptive and services jobs strictly in the order that they arrive. Although FCFS is simple to implement and ensures fairness, it can block several small jobs in the job queue when a job requesting more resources (large node count) is waiting for its request to be granted. FCFS also leads to fragmentation and longer wait times as nodes are not utilized efficiently (several nodes remain idle as the requirements of the next job cannot be met immediately).

There are also policies that do not dedicate nodes to jobs, such as gang scheduling (Feitelson and Jette, 1997; Setia et al., 1999; Batat and Feitelson, 2000). With gang scheduling, jobs can time-share nodes in a coordinated manner. That is, nodes are not exclusively allocated to a single job. Gang scheduling policies use explicit communication to relay global information and system state among participating jobs, leading to multiple points of failure and high overheads. Implicit coordinated scheduling policies that infer system state by observing local events have been proposed to address some of the aforementioned problems (Andrea Apraci-Dusseau, 1998). While these policies may improve utilization and overall job turnaround time in some cases, they are not considered to be a feasible option in supercomputing due to the high context-switching and paging costs involved.

Resource management policies also have to consider other aspects such as job priorities and user fairness. Scheduling policies may assign priorities to jobs, and provide these jobs a higher quality of service and faster turnaround times. Typically, in HPC systems, priorities are implemented with the help of separate job queues. All jobs in a particular job queue have the same scheduling priority. Queues with higher priorities are thus given preference. Scheduling policies also need to ensure fairness to all the users of the HPC facility. A policy is *fair-share* when it ensures that all the resources in the HPC system (nodes and power, for example) are equally distributed among all users of the system, and no users or jobs are given preferential treatment, unless they are associated with a higher priority.

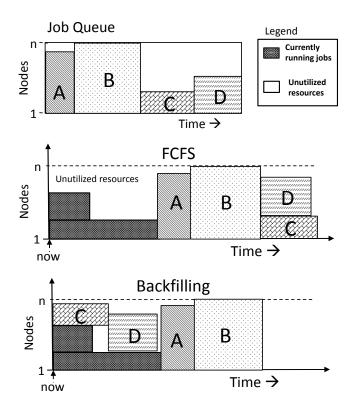

## 2.5.1 Backfilling

Backfilling algorithms (Lifka, 1995; Mu'alem and Feitelson, 2001; Skovira et al., 1996) address the problems of FCFS by executing smaller jobs out of order on the idle nodes while the next job (typically large) is waiting for resources. Backfilling is thus an optimization of the FCFS algorithm that improves utilization by moving smaller jobs forward, thus reducing job wait times for some jobs and in turn reducing the overall average turnaround time. Backfilling frequently uses a greedy algorithm that picks the first-fit from the job queue. The first-fit might not always be the best-fit, and a job further down the queue may be a better fit for the hole being backfilled. Finding the best-fit involves scanning the entire job queue, which increases job scheduling overhead significantly (Shmueli and Feitelson, 2003). Because of this, most practical resource managers use first-fit based backfilling.

A typical job queue for an HPC system is shown in Figure 2.4. Each job is represented by a box that depicts its requested node count and estimated runtime and the box area represents the size of a job. In our example, A is a modestly-sized job, and B and C are examples of large and small jobs respectively. Figure 2.4 also compares FCFS and backfilling. The y-axis in the figure represents available nodes, and the x-axis denotes real time (starting with the current time). While FCFS follows the order in which jobs arrive strictly, backfilling identifies opportunities to utilize the idle nodes by moving jobs C and D forward when job A is waiting for resources. This improves both node utilization as well as overall turnaround times.

There are two variants of backfilling—easy and conservative. Easy backfilling allows short jobs to move ahead and execute out of order as long as they do not delay the first queued job. Other jobs in the job queue may experience a delay with this scheme. Conservative backfilling, on the other hand, only lets short jobs to move ahead if they do not delay any queued job. Both variants make reservations for the queued jobs to avoid starvation (easy for the first and conservative for all). Easy backfilling is aggressive and greedy and attempts to maximize utilization at the current instant. Mu'alem et. al. (Mu'alem and Feitelson, 2001) compared and evaluated these two variants of backfilling

Figure 2.4: Comparison of FCFS and Backfilling

and concluded that they are similar in terms of performance, with easy backfilling doing slightly better than conservative backfilling for most workloads. Easy backfilling is thus preferred over conservative backfilling in practice. Researchers have also observed that for typical large HPC systems, enabling backfilling improves utilization by about 20% (Jackson et al., 2001).

Backfilling, though usually beneficial, does have some minor limitations. Because it runs jobs out of order, it may sometimes de-emphasize job priorities and user fairness in order to improve utilization. Also, in some scenarios, it introduces a *pseudo-delay* by adhering to a fixed reserved start time for a job and not letting the job run sooner as it normally would with FCFS. Pseudo-delay happens because users over-estimate job runtimes and provide poor inputs, and backfilling depends on these estimates for making reservations for the queued jobs.

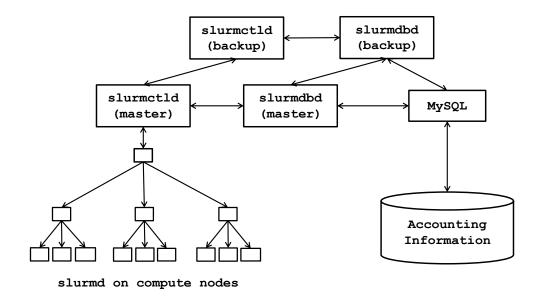

# 2.5.2 Simple Linux Utility for Resource Management (SLURM)

Simple Linux Utility for Resource Management, or SLURM, is an open source job scheduler that was primarily designed by Lawrence Livermore National Laboratory and SchedMD in 2002 (Yoo et al., 2003). Its main purpose is to simplify accessing resources on HPC clusters and to provide a standard framework for launching, managing and monitoring jobs executing on parallel machines. SLURM is a sophisticated batch scheduling system with half a million lines of code that is scalable, fault-tolerant, and portable. It is currently deployed on many of the world's fastest supercomputers and can be configured to use a particular scheduling algorithm with the help of plugins. The SLURM codebase includes several scheduling algorithms, such as FCFS, Backfilling, Gang Scheduling, and Multifactor Priority Scheduling.

For users, SLURM provides a set of tools such as salloc, srun, sacct, and scancel. These tools allow users to create, submit and modify job requests. For example, srun allows users to specify resource requirements for their job, such as the number of nodes, number of cores per node, job steps, memory usage, etc. For administrators, SLURM supports utilities such as scontrol and sacctmgr and provides various authentication, configuration and build options.

Figure 2.5: SLURM Architecture

Figure 2.5 depicts SLURM's architecture (Source: SchedMD). SLURM uses the slurmctld daemon ('controller') to monitor job queues and manage resource allocations. A single instance of this daemon typically runs on the head node of a cluster, along with the SLURM database daemon, slurmdbd. Slurmdbd is used for collecting accounting information (such as fair-share policies and priorities) with the help of a MySQL interface. Optional backup daemons for slurmctld and slurmdbd make the system fail-safe. Each compute node runs the slurmd daemon, which is primary used for launching tasks on a particular node. It communicates with the slurmctld daemon using RPC calls to indicate job status (for example: completed successfully, failed, killed by the user). Slurmd daemons support hierarchical communications with configurable fanout.

#### CHAPTER 3

#### HARDWARE OVERPROVISIONING

Several supercomputers today are targeted toward High Performance Linpack-like applications (Petitet et al., 2004) and designed to be worst-case provisioned—such that all nodes in the system can run at peak power simultaneously and HPC applications are assigned all the available power on a node. While this design strategy applies well for Linpack-like applications, several other scientific applications are unable to utilize the assigned peak power per node, resulting in limited performance under a power constraint. This chapter introduces hardware overprovisioning (or, overprovisioning for short) and explores its potential benefits when optimizing for application performance (execution time) under a power constraint. We analyze the performance of eight individual applications on a dedicated, 32-node system, and show that overprovisioning can improve performance (that is, execution time) under a power bound by up to 62% (2.63x) when compared to worst-case provisioning. The average improvement that we observe is 32% (1.47x). Section 3.1 introduces the motivation behind overprovisioning. Section 3.2 provides the details of the benchmarks and the system used in this study. Section 3.3 presents baseline results on a single node, and Section 3.4 presents our multi-node results at various system-level, global power bounds. Section 3.5 summarizes and concludes this chapter.

#### 3.1 Motivation for Overprovisioning

Traditionally, HPC systems are designed in a manner that all components (nodes) can operate at peak power simultaneously. Multiple-node scientific applications executing on such systems are assigned peak power on each active node by default. Going forward, when a global power constraint is enforced, such a worst-case provisioned design will limit the total number of nodes that the HPC system can use. As a

result, HPC application performance will also be limited as the application will have to possibly execute on fewer nodes. Also, because HPC application power and performance profiles can vary significantly, some applications may have different per-node power requirements. Such applications might not be able to utilize the assigned peak power per node and will result in underutilized and wasted power.

An overprovisioned system is a system with more capacity (nodes), with the caveat that we cannot simultaneously power all components at peak power because of strict power constraints. Such a system will be more flexible with regards to the total number of nodes that it can use, and can be reconfigured based on the characteristics of different applications.

The motivation for overprovisioning can be drawn from the processor architecture community. Modern multicore processor architectures support dynamic overclocking features such as Intel's Turbo Boost (Intel, 2008) and AMD's Turbo CORE (AMD, 2015). In such processors, the CPU frequency at which a core executes depends on the number of active cores, and not all cores can simultaneously run at the highest CPU frequency. Such processors are dynamically reconfigurable and adapt to the currently executing workload.

The same idea can be extended to multiple nodes in HPC systems. Exascale systems will have a power budget; the current bound set by the US Department of Energy is 20 MW. Overprovisioning in the supercomputing context means that not all nodes in the facility can execute at peak power simultaneously.

While overprovisioning means that the supercomputing center buys more compute capacity than can be used, it allows the user to customize the system to an application and thereby to achieve better performance under a power constraint by scheduling power carefully among resources. These resources include the racks in the machine room, the nodes within the racks, the components within a node, and the interconnect. A fixed system-level power-constraint on the cluster will hierarchically translate to application-level and node-level power-constraints.

As opposed to worst-case provisioning, overprovisioning is advantageous because it can allow both highly scalable and less scalable applications to perform well. This is because it supports reconfiguration and allocation of component power based on the application's characteristics. For example, an application's scalability determines whether we should use fewer nodes at higher power per node or more nodes at lower power per node under an application-level power constraint. In addition, depending on an application's CPU and memory usage, one can choose to use fewer cores per node or to allocate component power within a node (that is, power to the packages and the memory subsystem) based on utilization. Also, when only a few nodes in the application are on the critical path, running all nodes at peak power might be wasteful, and a different power allocation scheme might work better.

In order to explore overprovisioning and its effect on application performance, we solve the following question: given a machine with n nodes and c cores per node, a cluster-level power bound P on the machine, and a strongly-scaled HPC application, how important is choosing the *configuration* in minimizing execution time? We define a configuration as: (1) a value for n, (2) a value for c, (3) an amount of power p to be allocated to each node. The constraint is that the total power consumed must be no more than the bound P, and the goal is to minimize application runtime.

We explore this issue through a series of experiments on an Intel Sandy Bridge cluster at LLNL and use Intel's RAPL interface to enforce a range of power bounds on a diverse set of HPC applications and benchmarks. Thus, the cluster is effectively emulating an overprovisioned system.

#### 3.2 Experimental Setup

We now discuss the experiments used in our analysis. In this work, we report power values in Watts and timing information in seconds. We conduct our experiments on the *rzmerl* cluster at LLNL, which is a 162-node Sandy Bridge cluster. Each node is a Intel Sandy Bridge 062D server model (Intel Xeon E5-2690) with two PKG domains, and 8 cores per package. The memory per node is 32GB. The clock speed is 2.6 GHz, and the maximum turbo frequency is 3.3 GHz. The socket TDP is 115 W, and the minimum recommended power cap is 51 W. The cluster has a 32-node per job

limit. We use MVAPICH2 version 1.7 and compile all codes with the Intel compiler version 12.1.5. OpenMP threads are scheduled using the scatter policy by setting the KMP\_AFFINITY environment variable. While measurements are possible, power capping for PP0 and DRAM has been disabled by default by the system administrators. We run all experiments with power capping on the PKG domain with a single capping window and the shortest possible time window (0.000977 seconds). Thus, we avoid any potential large power spikes that might result when using larger time windows. We use four PKG power caps: 51 W; 65 W; 80 W; and 95 W. We run each configuration at least three times to mitigate noise. We disable Turbo Boost when power capping. We also run experiments with turbo enabled without using any RAPL-enforced power bounds. A cap of 115 W in our results represents this turbo mode. 115 W corresponds to the thermal limit on the PKG and, when we use turbo mode, this thermal limit becomes our power cap by default.

Our experiments use a hybrid MPI/OpenMP model. Hybrid models have low intra-node communication overhead and are more flexible in terms of configurations that we can test. Also, future architectures are likely to have many integrated cores on a single chip (for instance, Intel's MIC (Intel, 2012)). Because MPI processes have significant memory and communication overhead, the hybrid model is more likely than a flat MPI model. All applications are strongly scaled.

HPC Applications We use four HPC applications: SPhot (Lawrence Livermore National Laboratory, 2001) from the ASC Purple suite (Lawrence Livermore National Laboratory, 2002) and BT-MZ, SP-MZ, and LU-MZ from the NAS suite (Bailey, 2006). SPhot is a 2D photon transport code that uses a Monte Carlo approach to solve the Boltzmann transport equation by mimicking the behavior of photons as they move through different materials. SPhot is a CPU-bound, embarrassingly parallel application. For our multiple-node experiments, the input parameter nruns was set to 8192. For the single-node experiments, nruns was set to 1024. The NAS Multi-zone parallel benchmarks (NAS-MZ) are derived from Computational Fluid Dynamics (CFD) applications and are designed to evaluate the hybrid model. We use all three NAS-MZ

benchmarks: Block Tri-diagonal solver, or BT-MZ; Scalar Penta-diagonal solver, or SP-MZ; and Lower-Upper Gauss-Seidel solver, or LU-MZ. We use the Class C inputs.

Synthetic Benchmarks In order to cover the extreme cases in the application space, we also develop four MPI/OpenMP synthetic benchmarks. These tests are (1) CPU-bound and scalable (SC); (2) CPU-bound and not scalable (NSC); (3) Memory-bound and scalable (SM); (4) Memory-bound and not scalable (NSM). The CPU-bound benchmarks run a simple spin loop, and the Memory-bound benchmarks conduct a vector copy in reverse order. We control scalability by adding communication using MPI\_Alltoall() (i.e., fewer calls to MPI\_Alltoall() means better scalability).

#### 3.3 Single-Node, Baseline Results

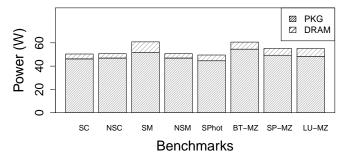

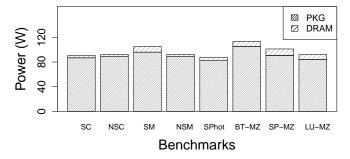

We first present details on the effect of power on our applications to understand the impact of power capping. We run our benchmarks on one node, varying the core count from 4 to 16. characteristics and their impact on configurations. Figure 3.1 shows the average PKG and DRAM power measured across the two sockets of the node for our benchmarks, at 4 and 16 cores and in turbo mode. We observe that some applications are more memory-intensive than others and hence consume more DRAM power. Examples of these are BT-MZ, SP-MZ, LU-MZ, and SM. At 16 cores per node, SP-MZ used 10.3% of its socket power for memory. Similarly, BT-MZ and LU-MZ use about 7-8% of their socket power for memory. SPhot, on the other hand, is relatively CPU intensive. We also observe that moving from 4 to 16 cores affects PKG power more than DRAM power. For instance, SPhot used 44.6 W of PKG power at 4 cores and 82.1 W of PKG power at 16 cores; DRAM power increased from 4.9 W to 5.7 W. Similarly, for BT-MZ, PKG power increased by 93% from 54.5 W to 105.7 W, but DRAM power only increased by 31%.

Figure 3.1 also shows that applications do not always use their allocated power. While the thermal limit on the PKG in turbo mode is 115 W, none of the applications actually use this much power, even when using all 16 cores. Most applications need between 80 and 90 W, except for BT-MZ, which uses nearly 106 W when running 16

# Average PKG and DRAM power per socket (16 cores per node)

Figure 3.1: Average PKG and DRAM Power Consumption Per Socket

cores. This results in both wasted power and reduced application performance. This important observation calls for efficient node-level power allocations.

Figure 3.2 shows the impact of varying the PKG power bound on the node on application performance at 4 and 16 cores per node for SPhot and SP-MZ. At 4 cores per node, neither of the applications uses more than 51 W of PKG power; thus, in an ideal situation, when Turbo Boost is disabled, application performance should be unaffected as we decrease power from 100 W to 51 W when running 4 cores. However, we observe a slight slowdown in performance of about 1-2% for our applications from 51 W to 100 W with 4 cores per node. Since we run each experiment at least three times to mitigate noise, we believe that the overhead introduced by Intel's RAPL algorithm (which is different at different power bounds) may cause this slowdown.

# Impact of varying the PKG–level power bound

Figure 3.2: Impact of Varying the PKG Power Cap on Execution Time

At 16 cores per node, our applications benefit from more power up to 85 W. Performance improved by 21.3% for SP-MZ and by 17.1% for SPhot. In turbo mode (115 W), all applications perform significantly better as they run at a higher CPU frequency. Performance for SPhot improved more than SP-MZ, primarily because SPhot is CPU-bound and less memory intensive.

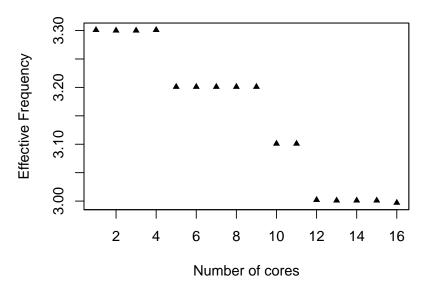

Next, we run single-node and multiple-node experiments with Turbo Boost to determine its effect on configurations. We collect samples every second with *librapl* and measure the frequency ratio by reading the APERF and MPERF MSRs (Intel, 2011). Figure 3.3 shows our results on a single-node with varying core count on our CPU-bound, scalable synthetic benchmark. We multiply the median frequency ratio value from the samples with the maximum non-turbo frequency (2.6 GHz) to determine the effective turbo frequency. Frequency ratios vary little across our samples.

Our results indicate that the effective turbo frequency depends on the number of active cores. Intel documentation (Intel, 2008) confirms this observation and also

mentions that the turbo frequency varies with temperature. We run our experiments at LLNL, where the machine room temperature is fairly constant over time and do not encounter any variation in the turbo frequency that could be attributed to temperature.

## **Results of Intel Turbo Boost (Single Node)**

Figure 3.3: Turbo Boost Example on a Single Node: CPU-bound and Scalable Micro-benchmark

We also run multiple-node experiments with Turbo Boost enabled and collect frequency samples every second with *librapl*. In these experiments, we use the same number of cores per node. All nodes reach the same turbo frequency, which is stable throughout the application's execution. All nodes engage in turbo mode similarly.

#### 3.4 Multi-node, Overprovisioning Results

This section presents and analyzes multiple-node results of the HPC applications and synthetic benchmarks. Because we could not feasibly run every possible configuration and because *rzmerl* has a 32-node limit per job, we run experiments with 8 to 32 nodes and 4 to 16 cores per node, in increments of 2. We assume uniform power allocation per node and that the applications are perfectly load-balanced.

#### 3.4.1 Configurations

As discussed previously, we define a configuration as: (1) a value for number of nodes, n, (2) a value for number of cores per node, c, and (3) power allocated per node, p, in Watts. We denote a configuration as  $(n \times c, p)$ . Because power capping is unavailable on DRAM and PP0, we use p to represent the PKG power that is allocated to the node. We measure DRAM power along with PKG power, and our results report their sum on each socket across all nodes when we report total power.

For comparison purposes, we define four special configurations: packed-max, packed-min, spread-max, and spread-min. The term packed denotes that a configuration uses all cores on one node before using an additional node, while spread denotes that processes are spread as evenly as possible across all nodes, with 4 being the fewest cores per node used. When max is appended, we use the maximum power (that is, turbo mode) on each node, while min means we use the minimum rated power (that is, cap at 51 Watts). In all four special configurations, we continue to add cores and/or nodes until we reach the global power bound (or until we cannot add more nodes).

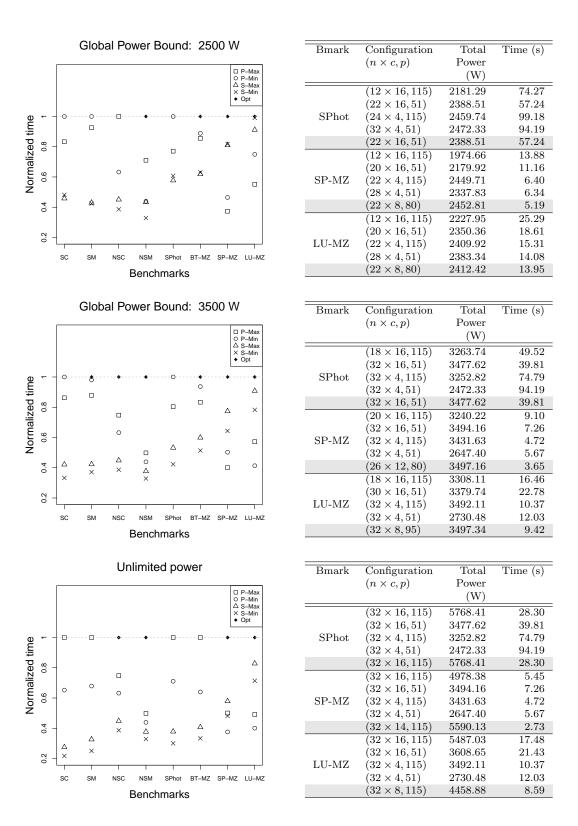

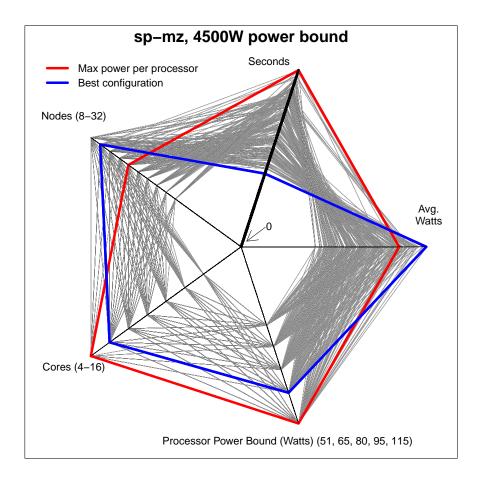

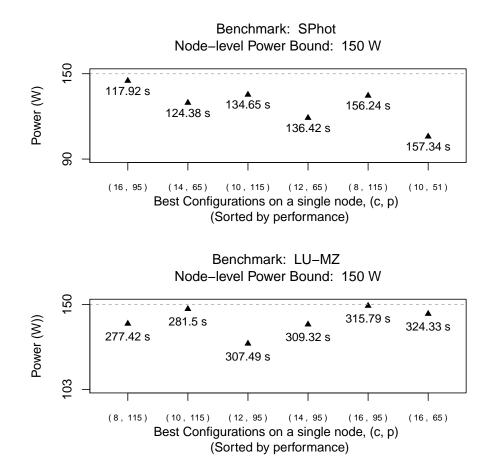

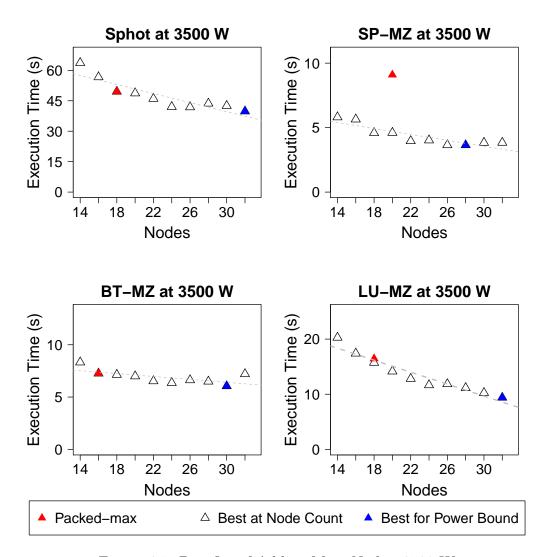

We run our benchmarks on multiple nodes under various overprovisioned scenarios. Our cluster of 32 nodes consumed about 6350 W of power when running all cores as fast as possible (based on BT-MZ data, which had the maximum power consumption). We investigate four overprovisioned scenarios; in each we have up to 32 nodes at our disposal, but power limits of 2500 W, 3000 W, 3500 W, and 4000 W. For comparison purposes, we also look at the case with unlimited power.